Index

organisation de la mémoire virtuelle, partage de pages, protection de pages, implémentation de la mémoire virtuelle (MMU), simple table de pages, tampon TLB

Avec la mémoire virtuelle, (VM - Virtual Memory), implémentée pour la première fois sur l’ordinateur ATLAS réalisé à l’université Manchester vers 1959 et développé pleinement avec la création du système d’exploitation MULTICS (frère aîné de l’UNIX), le programmeur peut concevoir des programmes nécessitant plus de mémoire que celle effectivement disponible.

La mémoire virtuelle est la technique de gestion de la mémoire pour tous les systèmes d’exploitation, en dehors des plus simples.

Organisation de la mémoire virtuelle

Plusieurs éléments caractérisent la mémoire virtuelle:

- une structure physique,

- une structure logique,

- la façon dont le système d’exploitation traduit une structure dans l’autre.

La mémoire physique (RAM) est constituée d’une série d’octets numérotés à partir de 0, jusqu’à la quantité de mémoire disponible dans le système.

La mémoire logique, appelée mémoire virtuelle, est la façon dont un programme voit la mémoire.

Un espace d’adressage virtuel est l’ensemble des adresses de mémoire disponibles pour un processus. Chaque processus a un espace d’adressage virtuel, généralement bien plus grand que la mémoire physique.

Bien que le nombre d’adresses physiques sur un ordinateur donné soit limité à la quantité de mémoire existante, le nombre d’adresses virtuelles n’est limité que par le nombre de bits constituant une adresse virtuelle.

Ainsi, le Pentium (adressage linéaire) et le Sparc, dont les adresses ont 32 bits, revendiquent un espace d’adressage virtuel de 232, soit quatre milliards d’octets (4 Goctets).

Du fait de la dissociation des espaces d’adressage physique et logique, un système de mémoire virtuelle doit accomplir deux tâches:

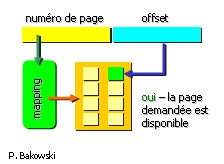

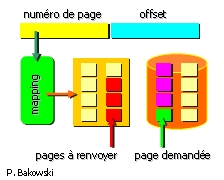

- traduire, ou mapper, un sous-ensemble des adresses virtuelles d’un processus en adresse de la mémoire physique: quand un processus lit ou écrit dans son espace d’adressage virtuel, le système de mémoire virtuelle utilise l’adresse virtuelle pour retrouver la bonne adresse physique avant de transférer les données/instructions; cette donnée/instruction peut ou non être disponible dans la partie RAM; en cas d’échec, ou défaut de page le système doit suspendre le processus et importer du disque l’information demandée.

- recopier une partie du contenu de la mémoire sur un disque quand il y a une trop grande demande de mémoire, c’est-à-dire lorsqu’un processus tente d’utiliser plus de mémoire que celle physiquement disponible.

L’association entre les adresses virtuelles et physiques, et le transfert de données entre l’espace de stockage et la mémoire physique sont les tâches principales d’un système de mémoire virtuelle, ce dernier devant également offrir d’autres services:

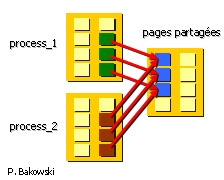

- permettre le partage de la mémoire entre deux processus de façon aisée et efficace,

- protéger la mémoire partagée et privée contre les accès non autorisés,

- répondre aux défauts de page de plusieurs processus à la fois, pour des systèmes multiprocesseurs.

De même, si deux processus collaborent pour la création d’un tampon de mémoire partagée, l’espace d’adressage virtuel de chacun peut être associé aux mêmes pages physiques occupées par le tampon. Les pages du tampon sont marquées en lecture-écriture.

Protection de la mémoire virtuelle

- Il y a trois formes de protection de la mémoire dans la plupart des systèmes d’exploitation modernes:

un espace d’adressage différent pour chaque processus;

le matériel empêche l’accès par un processus à l’espace d’adressage virtuel d’un autre processus;

- deux modes de fonctionnement:

* le mode noyau, où les processus peuvent accéder au code et aux données du système,

* le mode utilisateur, où cela n’est pas possible;

- un mécanisme de protection des pages:

à chaque page virtuelle est associé un ensemble d’indicateurs qui précisent les types d’accès autorisés en mode utilisateur et en mode noyau.

* lecture seule

* lecture/écriture

* exécution seule (execute-only)

* pas d’accès (no-access)

* copie à l’écriture (copy on write)

* page de garde - contrôle automatique des limites sur les piles

Implémentation de la mémoire virtuelle dans les processeurs

La gestion de la mémoire virtuelle est dévolue à une unité fonctionnelle spécifique - MMU (Memory Management Unit). Le MMU gére l’espace virtuel de taille fixée par le nombre de bits d’adresse virtuelle (e.g. 32). Dans l’espace virtuel linéaire (MIPS R3000, SunSPARC, Pentium), l’adresse virtuelle est identique à l’adresse effective issue du processeur. Dans l’espace segmenté (cas du IBM POWER), la taille de l’adresse virtuelle est une composition (concaténation) de la taille d’une adresse initiale pour le processus donné et d’un registre de segment. Par exemple dans IBM POWER l’adresse virtuelle est de taille 52 bits: (32-4) + 24 = 52 où 4 bits servent à la numérotation d’un des 16 registres segments, la taille de chaque registre segment est 24 bits.

Afin que plusieurs processus puissent co-exister en mémoire principale, seules les pages utiles à l’exécution du programme à un instant donné sont présentes en mémoire principale. Pour la grande majorité de processeurs, la dimension de la page est 4 Koctets. En principe, à une même adresse logique issue de deux processus différents doivent correspondre deux adresses physiques distinctes, les exceptions sont le code ou les données partagées.

Les adresses virtuelles sont traduites en adresses physiques par le système d’exploitation grâce à une instruction privilégiée. Cette instruction a accès à la table de pages. Pour une mémoire virtuelle de 4 Goctets, la table de pages comprend 1 millon d’entrées et nécessite 4 Moctets au minimum; une telle taille est prohibitive si plusieurs processus co-existent en mémoire principale. Pour résoudre ce problème (MIPS, Pentuim), la table de pages est elle même localisée en mémoire virtuelle.

Comme exemple d’implémentation prenons les processeurs MIPS ou Pentium. Dans ces processeurs l’espace virtuel est disposé sur un niveau de pagination. L’architecture porte jusqu’à 64 processus simultanés dont 64 tables de pages sont situées dans la mémoire virtuelle paginée.

Tampon de traduction d’adresses

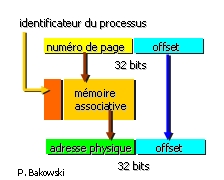

Chaque lecture de table de pages exige un accès à la mémoire et la recherche de l’adresse physique peut se prolonger sur plusieurs cycles. Afin d’éviter cette recherche lors de chaque accès à la mémoire paginée, il est intéressant de conserver les dernières traductions (relations - adresse virtuelle <-> adresse physique) dans une mémoire associative appelée TLB (translation lookaside buffer). Chaque fois que le processeur produit une adresse virtuelle, celle-ci est comparée aux adresses utiles stockées dans le tampon TLB pour déterminer si la traduction est disponible.

Implémentation du tampon TLB

Prenons comme exemple les processeurs SunSPARC et MIPS R3000. Le TLB de ces processeurs est de taille 64 entrées. L’associativité totale des TLB des SunSPARC et MIPS R3000 nécessite la mise en oeuvre d’un algorithme de remplacement après un échec. Les deux processeurs utilisent un algorithme de type aléatoire mis en oeuvre à partir d’un compteur 6 bits qui pointe vers une entrée. Le compteur est incrementé au rythme de l’horloge interne. Sachant qu’une adresse virtuelle est relative à un processus, il existe une ambiguïté quant au contenu de la traduction.

Deux solution sont possibles:

- la purge totale du TLB à chaque changement de contexte,

- l’ajout d’un identificateur de processus à l’adresse virtuelle dans la table de correspondance - cette solution a été implantée dans les deux processeurs étudiés.

Aux numéros physiques des pages enregistrées dans le tampon TLB sont ajoutées des informations relatives à la page. Le bit d’indication d’écriture signifie que la page a été utilisée en écriture. Cette information doit être recopiée dans l’entrée de table de pages correspondante pour que le système d’exploitation sauvegarde la page affectée sur le disque lors du remplacement. Cette opération doit être réalisée par le matériel.

Tampons TLB et l’adressage de caches

L’adressage des caches peut être virtuel ou physique. Par exemple, le processeur SunSPARC a un cache virtuel. Chaque fois que l’unité entière émet une adresse virtuelle, le cache et le TLB sont sollicités simultanément. Si l’accès au cache est un succès, l’adresse physique qui est éventuellement dans le TLB est ignorée. Le processeur MIPS R3000 a un cache physique. Cela nécessite la transformation des adresses virtuelles en adresses physiques avant l’accès au cache.Le cache virtuel permet de réduire le temps de traduction dans la recherche d’une instruction ou d’une donnée. En contrepartie, les informations contenues dans le TLB doivent être dupliquées dans le cache afin d’assurer la cohérence entre cache, TLB et tables de pages.